## Accélérateurs de calculs Évolution des architectures haute-performance

Sylvain HENRY

sylvain.henry@labri.fr

Version 1.2 - 20 novembre 2012

## Sommaire

- Introduction

- Historique

- Les accélérateurs

- Programmation des accélérateurs

- 2 Quelques exemples d'accélérateurs

- IBM CELL BroadBand Engine

- Cartes graphiques (GPU)

- Architectures hybrides GPU-CPU

- Modèles de programmation

- Bas niveau : graphe de commandes

- Abstractions

## Lignes directrices

- Introduction

- Historique

- Les accélérateurs

- Programmation des accélérateurs

- Quelques exemples d'accélérateurs

- IBM CELL BroadBand Engine

- Cartes graphiques (GPU)

- Architectures hybrides GPU-CPU

- Modèles de programmation

- Bas niveau : graphe de commandes

- Abstractions

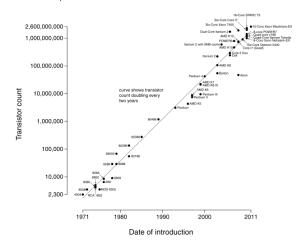

# Loi de Moore

#### Le nombre de transistors des microprocesseurs double tous les 2 ans

#### Microprocessor Transistor Counts 1971-2011 & Moore's Law

#### Loi de Moore

Que faire de l'espace libéré (i.e. avec les nouveaux transistors)?

- Multiplier le nombre d'unités

- Architectures super-scalaires

- Unités vectorielles (SIMD)

- Multiplier le nombre de cœurs

- Architectures multi-cœurs

- Architectures multi-mémoires (NUMA)

- 3 Complexifier l'architecture

- Out-of-order

- Hiérarchie de caches améliorée (dimensions, nombre de niveaux...)

- 3 Prédiction de branchement et exécution spéculative

- Renommage de registres

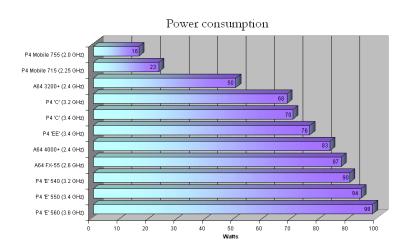

#### Limitations

#### Consommation énergétique et dissipation thermique

#### Limitations

Plus le nombre de cœurs augmente...

- Concurrence pour l'accès à la mémoire

- Coût des mécanismes de cohérence de cache

- Coût des mécanismes pour simuler une seule mémoire globale

- Héritage des architectures de type Von Neumann

- Plusieurs mémoires physiques

- Les applications ne « voient » qu'une mémoire

#### Problème

Ne passe pas à l'échelle (plusieurs centaines, milliers de cœurs?)

#### Limitations

Plus le nombre de cœurs augmente...

- Concurrence pour l'accès à la mémoire

- Coût des mécanismes de cohérence de cache

- Coût des mécanismes pour simuler une seule mémoire globale

- Héritage des architectures de type Von Neumann

- Plusieurs mémoires physiques

- Les applications ne « voient » qu'une mémoire

#### Problème

Ne passe pas à l'échelle (plusieurs centaines, milliers de cœurs?)

### Solutions?

- Architectures sans cohérence de cache

- nccNUMA: non cache-coherent NUMA (vs ccNUMA)

- Ne met en cache que la mémoire locale

- Accès mémoires distantes plus chers

- Architectures spécialisées

- Digital Signal Processor (DSP), systolic arrays, etc.

- Accélérateurs de calculs

- Les différentes mémoires physiques sont gérées explicitement par les applications

- Cœurs moins rapides mais beaucoup (beaucoup) plus nombreux

Dans tous les cas : changer assez radicalement d'architecture

### Solutions?

- Architectures sans cohérence de cache

- nccNUMA: non cache-coherent NUMA (vs ccNUMA)

- Ne met en cache que la mémoire locale

- Accès mémoires distantes plus chers

- Architectures spécialisées

- Digital Signal Processor (DSP), systolic arrays, etc.

- Accélérateurs de calculs

- Les différentes mémoires physiques sont gérées explicitement par les applications

- Cœurs moins rapides mais beaucoup (beaucoup) plus nombreux

Dans tous les cas : changer assez radicalement d'architecture

## Lignes directrices

- Introduction

- Historique

- Les accélérateurs

- Programmation des accélérateurs

- Quelques exemples d'accélérateurs

- IBM CELL BroadBand Engine

- Cartes graphiques (GPU)

- Architectures hybrides GPU-CPU

- Modèles de programmation

- Bas niveau : graphe de commandes

- Abstractions

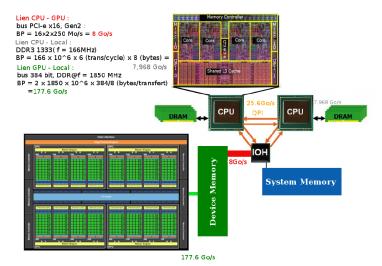

#### Les accélérateurs

- Architectures hétérogènes

- 1 ou plusieurs cœurs « classiques »

- Plusieurs cœurs spécialisés (vectoriels en général)

- Plusieurs mémoires

- Lien entre la mémoire de l'hôte et celles des accélérateurs

- PCI Express

- Lien spécifique

- Exemples

- IBM CELL BroadBand Engine

- Cartes graphiques

- Architectures hybrides GPU/CPU (Intel MIC, AMD Fusion...)

## Exemple d'architecture avec un accélérateur

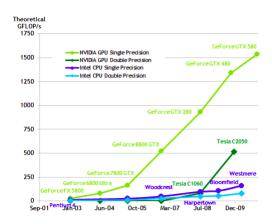

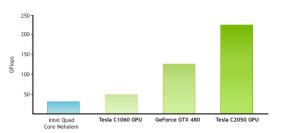

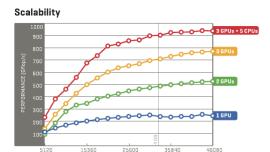

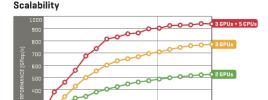

# Performances Performances théoriques (source NVIDIA)

# Performances Sur un exemple de code N-Body (source NVIDIA)

N-Body, Double Precision, n= 107,520

Performances N-body sur les CPU x86 avec plusieurs types de GPU

## Top500 Classement de juin 2012

| Rank | Site                                                                        | Computer/Year Vendor                                                                                                 | Cores   | R <sub>max</sub> | R <sub>peak</sub> | Power   |

|------|-----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|---------|------------------|-------------------|---------|

| 1    | DOE/NINSA/LLNL<br>United States                                             | Sequoia - BlueGene/Q,<br>Power BQC 16C 1.60 GHz,<br>Custom / 2011<br>IBM                                             | 1572864 | 16324.75         | 20132.66          | 7890.0  |

| 2    | RIKEN Advanced<br>Institute for<br>Computational Science<br>(AICS)<br>Japan | K computer, SPARC64 VIIfx<br>2.0GHz, Tofu interconnect /<br>2011<br>Fujitsu                                          | 705024  | 10510.00         | 11280.38          | 12659.9 |

| 3    | DOE/SC/Argonne<br>National Laboratory<br>United States                      | Mira - BlueGene/Q, Power<br>BQC 16C 1.60GHz, Custom /<br>2012<br>IBM                                                 | 786432  | 8162.38          | 10066.33          | 3945.0  |

| 4    | Leibniz Rechenzentrum<br>Germany                                            | SuperMUC - iDataPlex<br>DX360M4, Xeon E5-2680 8C<br>2.70GHz, Infiniband FDR /<br>2012<br>IBM                         | 147456  | 2897.00          | 3185.05           | 3422.7  |

| 5    | National<br>Supercomputing Center<br>in Tranjin<br>China                    | Tianhe-1A - NUDT YH MPP,<br>Xeon X5670 6C 2.93 GHz,<br>NVIDIA 2050 / 2010<br>NUDT                                    | 186368  | 2566.00          | 4701.00           | 4040.0  |

| 6    | DOE/SC/Oak Ridge<br>National Laboratory<br>United States                    | Jaguar - Cray XK6, Opteron<br>6274 16C 2.2003Hz, Cray<br>Gemini interconnect, NVIDIA<br>2090 / 2009<br>Cray Inc.     | 298592  | 1941.00          | 2627.61           | 5142.0  |

| 7    | CINECA                                                                      | Fermi - BlueGene/Q, Power<br>BQC 16C 1.60GHz, Custom /<br>2012<br>IBM                                                | 163840  | 1725.49          | 2097.15           | 821.9   |

| 8    | Forschungszentrum<br>Juelich (FZJ)<br>Germany                               | JuqUEEN - BlueGene/Q,<br>Pawer BQC 16C 1.60GHz,<br>Custom / 2012<br>IBM                                              | 131072  | 1380.39          | 1677.72           | 657.5   |

| 9    | CEA/TGCC-GENCI<br>France                                                    | Curle thin nodes - Bullx<br>B510, Xeon E5-2880 8C<br>2.700GHz, Infiniband QDR /<br>2012<br>Bull                      | 77184   | 1359.00          | 1667.17           | 2251.0  |

| 10   | National<br>Supercomputing Centre<br>in Shenzhen (NSCS)<br>China            | Nebulae - Dawning TC3600<br>Blade System, Xeon X5650<br>6C 2.66GHz, Infiniband QDR,<br>NVIDIA 2050 / 2010<br>Dawning | 120640  | 1271.00          | 2984.30           | 2580.0  |

## Lignes directrices

- Introduction

- Historique

- Les accélérateurs

- Programmation des accélérateurs

- Quelques exemples d'accélérateurs

- IBM CELL BroadBand Engine

- Cartes graphiques (GPU)

- Architectures hybrides GPU-CPU

- Modèles de programmation

- Bas niveau : graphe de commandes

- Abstractions

#### Gestion mémoire

- Manuelle et explicite

- transferts asynchrones (DMA)

- pas de pagination

- pas de mécanisme de swap

- Scratchpads

- gérés explicitement

- parfois partagés

- pas de mécanisme de cohérence avec la mémoire globale

- Capacité mémoire faible

- parfois quelques kilo-octets par cœur

- Contraintes similaires aux systèmes embarqués

#### Gestion mémoire

- Manuelle et explicite

- transferts asynchrones (DMA)

- pas de pagination

- pas de mécanisme de swap

- Scratchpads

- gérés explicitement

- parfois partagés

- pas de mécanisme de cohérence avec la mémoire globale

- Capacité mémoire faible

- parfois quelques kilo-octets par cœur

- Contraintes similaires aux systèmes embarqués

### Gestion mémoire

- Manuelle et explicite

- transferts asynchrones (DMA)

- pas de pagination

- pas de mécanisme de swap

- Scratchpads

- gérés explicitement

- parfois partagés

- pas de mécanisme de cohérence avec la mémoire globale

- Capacité mémoire faible

- parfois quelques kilo-octets par cœur

- Contraintes similaires aux systèmes embarqués

- Différents modèles/langages de programmation

- SIMD, SPMD...

- Différents compilateurs et plusieurs binaires par application

- Chargement explicite des binaires sur l'accélérateur

- Retour d'anciennes techniques

- « Code overlay » lorsque la mémoire est insuffisante pour contenir le code complet du programme

- Différents modèles/langages de programmation

- SIMD, SPMD...

- Différents compilateurs et plusieurs binaires par application

- Chargement explicite des binaires sur l'accélérateur

- Retour d'anciennes techniques

- « Code overlay » lorsque la mémoire est insuffisante pour contenir le code complet du programme

- Différents modèles/langages de programmation

- SIMD, SPMD...

- Différents compilateurs et plusieurs binaires par application

- Chargement explicite des binaires sur l'accélérateur

- Retour d'anciennes techniques

- « Code overlay » lorsque la mémoire est insuffisante pour contenir le code complet du programme

- Différents modèles/langages de programmation

- SIMD, SPMD...

- Différents compilateurs et plusieurs binaires par application

- Chargement explicite des binaires sur l'accélérateur

- Retour d'anciennes techniques

- « Code overlay » lorsque la mémoire est insuffisante pour contenir le code complet du programme

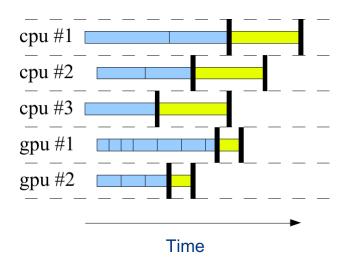

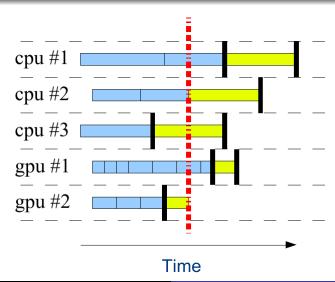

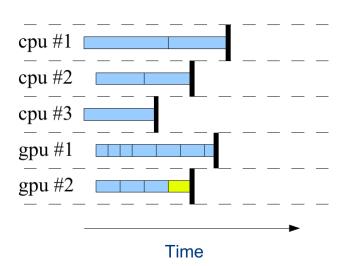

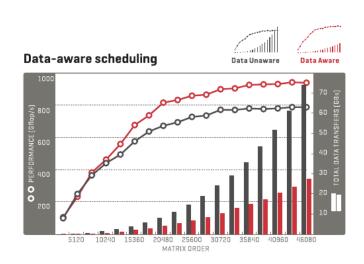

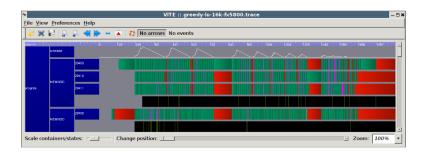

## Aspect distribué

- Similaire à l'utilisation d'un réseau de machines

- Recouvrir les communications par le calcul

- Limiter/optimiser les transferts

- Placer les tâches à proximité des données qu'elles utilisent

- Équilibrage de charge

- Quel type de tâche donner à chaque type de cœur?

- Différences entre architectures à prendre en compte

- Boutisme (endianness), alignements...

## Aspect distribué

- Similaire à l'utilisation d'un réseau de machines

- Recouvrir les communications par le calcul

- Limiter/optimiser les transferts

- Placer les tâches à proximité des données qu'elles utilisent

- Équilibrage de charge

- Quel type de tâche donner à chaque type de cœur?

- Différences entre architectures à prendre en compte

- Boutisme (endianness), alignements...

## Aspect distribué

- Similaire à l'utilisation d'un réseau de machines

- Recouvrir les communications par le calcul

- Limiter/optimiser les transferts

- Placer les tâches à proximité des données qu'elles utilisent

- Équilibrage de charge

- Quel type de tâche donner à chaque type de cœur?

- Différences entre architectures à prendre en compte

- Boutisme (endianness), alignements...

## Lignes directrices

- Introduction

- Historique

- Les accélérateurs

- Programmation des accélérateurs

- 2 Quelques exemples d'accélérateurs

- IBM CELL BroadBand Engine

- Cartes graphiques (GPU)

- Architectures hybrides GPU-CPU

- Modèles de programmation

- Bas niveau : graphe de commandes

- Abstractions

## IBM CELL BroadBand Engine

- Alliance entre Sony, Toshiba et IBM

- 4 années de développement, début en 2001

- 1 cœur de type Power4 simplifié (in-order) + 8 cœurs vectoriels

- Très bon rapport performance/consommation

- Supercalculateur RoadRunner

- 6,120 Opteron (2 cœurs) + 12,240 PowerXCell 8i (9 cœurs)

- En 2008, 1er du Top500 et 4e au Green500

- PlayStation 3 (2005)

- Succés commercial

- Accès « grand public » à l'architecture

## IBM CELL BroadBand Engine

- Alliance entre Sony, Toshiba et IBM

- 4 années de développement, début en 2001

- 1 cœur de type Power4 simplifié (in-order) + 8 cœurs vectoriels

- Très bon rapport performance/consommation

- Supercalculateur RoadRunner

- 6,120 Opteron (2 cœurs) + 12,240 PowerXCell 8i (9 cœurs)

- En 2008, 1er du Top500 et 4e au Green500

- PlayStation 3 (2005)

- Succés commercial

- Accès « grand public » à l'architecture

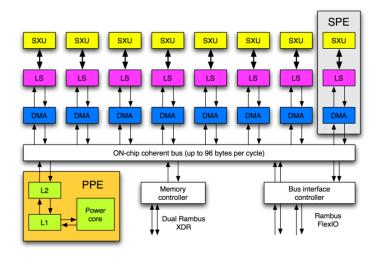

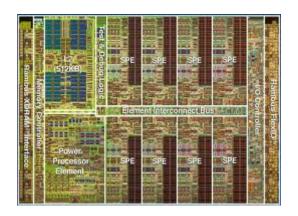

# IBM CELL BroadBand Engine

- Alliance entre Sony, Toshiba et IBM

- 4 années de développement, début en 2001

- 1 cœur de type Power4 simplifié (in-order) + 8 cœurs vectoriels

- Très bon rapport performance/consommation

- Supercalculateur RoadRunner

- 6,120 Opteron (2 cœurs) + 12,240 PowerXCell 8i (9 cœurs)

- En 2008, 1er du Top500 et 4e au Green500

- PlayStation 3 (2005)

- Succés commercial

- Accès « grand public » à l'architecture

#### Schéma de l'architecture

## Caractéristiques

- PPE (Power Processor Element)

- Dual-cœur, in-order

- L1 64ko L2 512ko

- SPE (x8, Synergistic Processing Element)

- Uni-cœur, in-order

- 128 registres de 128bits (SIMD)

- Local store 256ko (LS, scratchpad, code + données)

- 1 contrôleur DMA

- EIB (Element Interconnect Bus)

- Mémoire

## Aspect physique

## Super-calculateur RoadRunner

# Cluster PS3 Cluster de test de l'US Air Force (336 PS3)

#### Programmation

- Context d'exécution

- Exécution d'un programme sur un SPE

- Une fois actif, le reste jusqu'à la fin du programme

- Pas plus de 1 context actif par SPE

- Étapes sur l'hôte

- Création de context : spe create context

- Chargement d'un programme : spe load program

- Exécution du programme : spe\_context\_run (bloquante)

### Programmation Exemple de code hôte

```

#include <libspe2.h>

extern spe program handle t mon kernel;

char buffer[128];

int main() {

int entry = SPE DEFAULT ENTRY;

int nb spe = spe cpu info get(SPE COUNT USABLE SPES, -1);

spe_context_ptr_t context = spe_context_create(0, NULL);

spe program load(context, &mon kernel);

spe context run(context, &entry, 0, buffer, (void*)128, NULL);

spe context destroy(context);

return 0:

```

# Programmation Exemple de code SPE

```

#include <spu_mfcio.h>

int main(unsigned int speid, unsigned long long argp, unsigned long long envp) -

char buffer[128] __attribute__((aligned(128)));

int tag = 1, tag_mask = 1<<tag;

mfc_get(buffer,(unsigned int) argp, envp, tag, 0, 0);

mfc_write_tag_mask(tag_mask);

mfc_read_tag_status_all();

return 0;

}</pre>

```

#### Lignes directrices

- Introduction

- Historique

- Les accélérateurs

- Programmation des accélérateurs

- 2 Quelques exemples d'accélérateurs

- IBM CELL BroadBand Engine

- Cartes graphiques (GPU)

- Architectures hybrides GPU-CPU

- Modèles de programmation

- Bas niveau : graphe de commandes

- Abstractions

# Cartes graphiques programmables (GPGPU) General-Purpose computing on Graphics Processing Units (GPGPU)

- Quasiment toutes les machines sont équipées

- Programmables par le biais des shaders (pixel shaders, vertex shaders...)

- Architectures massivement parallèles

- calcul indépendant pour chaque sommet, chaque pixel, etc.

- Utilisation détournée pour faire des calculs non graphiques

- Render-to-texture (RTT) plutôt qu'affichage à l'écran

- Gains de performances notables (x20...)

- Pipeline graphique programmable (3 niveaux)

- pixel shaders

- vertex shaders

- geometry shaders

- Utilisation détournée pour le calcul non graphique

- Difficile car les API (e.g. OpenGL, Cg) ne sont pas prévues pour ca

- Difficulté pour équilibrer la charge des 3 niveaux

- Performance et faible consommation

- Threads indépendants

- Plusieurs bancs mémoire

#### Programmation

Exemple de code Cg (source Wikipedia)

```

struct VertIn {

: POSITION:

float4 pos

float4 color : COLOR0:

}:

struct VertOut {

float4 pos : POSITION;

float4 color : COLORO:

};

// vertex shader main entry

VertOut main(VertIn IN, uniform float4x4 modelViewProj) {

VertOut OUT:

= mul(modelViewProj, IN.pos);

OUT. pos

// calculate output coords

OUT. color = IN. color:

// copy input color to output

OUT. color.z = 1.0 f:

// blue component of color = 1.0 f

return OUT:

}

```

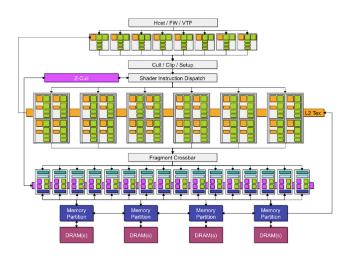

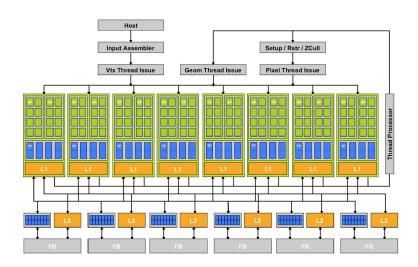

- Architecture unifiée « Unified Shader Architecture »

- 8 cœurs contenant chacun 16 PE (Processing Element)

- Les PE peuvent effectuer les trois types de shaders précédents

- Introduction de CUDA : Compute Unified Device Architecture

- Langage proche du C pour le code exécuté sur le GPU

- Extensions C/C++ pour programmer facilement les exécutions depuis le code hôte

- Architecture Tesla

- « GPU » sans sortie graphique

- Dédiée au calcul

- Architecture unifiée « Unified Shader Architecture »

- 8 cœurs contenant chacun 16 PE (Processing Element)

- Les PE peuvent effectuer les trois types de shaders précédents

- Introduction de CUDA : Compute Unified Device Architecture

- Langage proche du C pour le code exécuté sur le GPU

- Extensions C/C++ pour programmer facilement les exécutions depuis le code hôte

- Architecture Tesla

- « GPU » sans sortie graphique

- Dédiée au calcul

- Architecture unifiée « Unified Shader Architecture »

- 8 cœurs contenant chacun 16 PE (Processing Element)

- Les PE peuvent effectuer les trois types de shaders précédents

- Introduction de CUDA : Compute Unified Device Architecture

- Langage proche du C pour le code exécuté sur le GPU

- Extensions C/C++ pour programmer facilement les exécutions depuis le code hôte

- Architecture Tesla

- « GPU » sans sortie graphique

- Dédiée au calcul

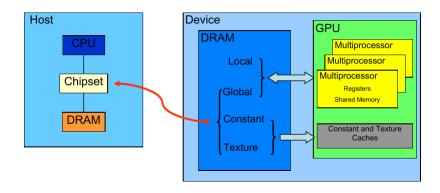

# Architecture NVIDIA Modèle mémoire CUDA

#### Architecture NVIDIA Modèle d'exécution CUDA

#### Software

#### Hardware

Thread Block

Multiprocessor

Grid

Processor array

Les différentes mémoires et leurs propriétés

| Memory   | Location | Cached | Access | Scope                  | Lifetime    |

|----------|----------|--------|--------|------------------------|-------------|

| Register | On-chip  | N/A    | R/W    | One thread             | Thread      |

| Local    | Off-chip | No     | R/W    | One thread             | Thread      |

| Shared   | On-chip  | N/A    | R/W    | All threads in a block | Block       |

| Global   | Off-chip | No     | R/W    | All threads + host     | Application |

| Constant | Off-chip | Yes    | R      | All threads + host     | Application |

| Texture  | Off-chip | Yes    | R      | All threads + host     | Application |

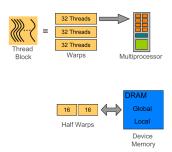

#### Architecture NVIDIA Modèle d'exécution CUDA : les warps

- Blocs de threads décomposés en « Warps » de 32 threads

- Les threads d'un warp sont exécutés physiquement en parallèle (SIMD)

- Accès à la mémoire globale en une transaction par demi-wrap (16 threads) en cas de coalescence

Accès mémoire globale coalescent : Compute Capability 1.0 et 1.1

Out of sequence – 16 transactions

Coalesces – 1 transaction

Misaligned – 16 transactions

Accès mémoire globale coalescent : Compute Capability 1.2

1 transaction - 64B segment

2 transactions - 64B and 32B segments

1 transaction - 128B segment

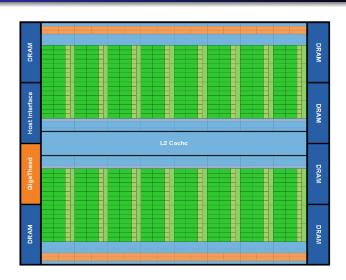

Fermi : hiérarchie mémoire (cache L1 configurable + cache L2)

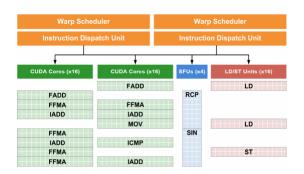

- Plusieurs SM (Streaming Multiprocessor)

- contenant chacun 32 cœurs

- 16 unités LOAD/STORE : accès aux différents bancs mémoire

- le nombre de SM dépend... du prix de la carte

- 32 instructions par cycle sur 2 des 4 blocs d'exécution

- les instructions proviennent de 2 warps

- 1 warp est un ensemble de 32 threads

Fermi : exécution concurrente de kernels

Kernel1

Serial Kernel Execution

Concurrent Kernel Execution

# Architecture NVIDIA Kepler

# Architecture NVIDIA Kepler

- 192 cœurs par SMX (streaming multiprocessor extreme)

- « Dynamic Parallelism »

- Le tâches exécutées sur le GPU peuvent soumettre d'autres tâches

- Moins de contrôle effectué par le CPU

- Diminue le nombre de transferts sur le lien PCI Express

- Plus de coeurs, moins rapides

- Meilleur rapport performance/consommation (x3 annoncé)

#### Architecture AMD/ATI

Anciennes architectures

- VLIW (Very Long Instruction Word)

- Bundles d'instructions indépendantes formés par le compilateur

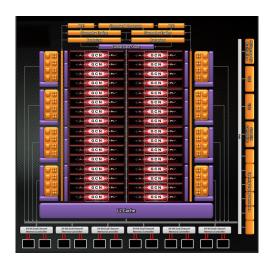

# Architecture AMD/ATI Radeon HD 7970 « Tahiti »

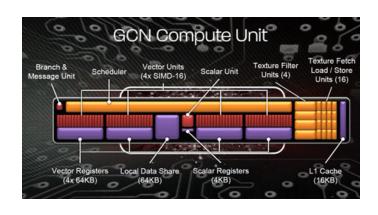

# Architecture AMD/ATI Graphics Core Next (GCN) architecture

#### Lignes directrices

- Introduction

- Historique

- Les accélérateurs

- Programmation des accélérateurs

- 2 Quelques exemples d'accélérateurs

- IBM CELL BroadBand Engine

- Cartes graphiques (GPU)

- Architectures hybrides GPU-CPU

- Modèles de programmation

- Bas niveau : graphe de commandes

- Abstractions

#### Architectures hybrides GPU-CPU

- Intel ne veut par perdre son avantage face aux GPU

- Architectures hybrides: ISA x86 avec architecture type GPU

- Prototypes : Larrabee, SCC, MIC

- Achat de concurrents (e.g. RapidMind)

- Argument : plus simple à programmer (mêmes outils que sur CPU)

- Réaction de AMD

- Fusion / Heterogeneous Systems Architectures (HSA)

- Achat d'ATI en 2006

#### Intel Xeon Phi / MIC

Intel Many Integrated Core architecture (MIC)

• Plus d'informations après Super Computing 2012

#### Lignes directrices

- Introduction

- Historique

- Les accélérateurs

- Programmation des accélérateurs

- Quelques exemples d'accélérateurs

- IBM CELL BroadBand Engine

- Cartes graphiques (GPU)

- Architectures hybrides GPU-CPU

- Modèles de programmation

- Bas niveau : graphe de commandes

- Abstractions

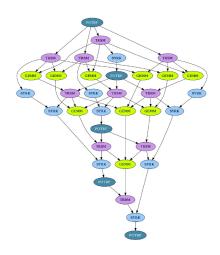

#### Bas niveau : graphe de commandes Ce que l'application doit gérer

- Gestion mémoire

- Allocation d'espaces dans les mémoires

- Transferts de données entre les mémoires

- Programmation des contrôleurs DMA

- Libération des espaces alloués

- Gestion des codes

- Compilation pour les différents types de cœurs

- Transfert/chargement des binaires

- Placement et ordonnancement

#### Frameworks Frameworks utilisant ce modèle

- Bibliothèque SPE : programmation bas niveau du CELL BE

- CUDA: spécifique aux cartes graphiques NVidia

- CUDA + Ocelot : cible aussi les CPUs

- CAL : spécifique aux cartes graphiques ATI/AMD

- Bibliothèque NUMA : programmation sur architectures NUMA

- OpenCL : nouveau standard censé unifier tous les autres

### Standards OpenCL et CUDA... (source : http://xkcd.com/927/)

HOW STANDARDS PROLIFERATE: (SEE: A/C CHARGERS, CHARACTER ENCODINGS, INSTANT MESSAGING, ETC.)

SITUATION: THERE ARE 14 COMPETING STANDARDS.

# Open Computing Language

- Spécification du Khronos Group pour le calcul sur architectures hétérogènes

- AMD/ATI, Apple, Intel, NVIDIA, SGI...

- Première version en 2008

- Dernière version à ce jour : version 1.2 le 15 novembre 2011

- Fortement inspiré par CUDA de NVIDIA (propriétaire)

- Disponible pour plusieurs accélérateurs et CPU

- Spécifie

- Une API pour l'hôte, i.e. l'application qui contrôle les accélérateurs

- Un langage avec lequel programmer les kernels exécutés sur les accélérateurs

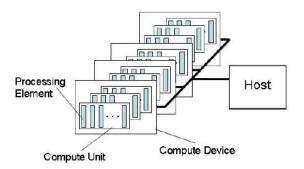

### OpenCL Modèle global

• Un hôte connecté à un ou plusieurs « compute devices »

#### OpenCL Modèle d'exécution

- Un programme exécuté sur l'hôte

- Gère l'exécution des kernels

- Les kernels (noyaux de calcul) exécutés sur les accélérateurs

- Un espace d'indices est défini lors de leur exécution

- 1, 2 ou 3 dimensions

- Pour chaque indice, une instance du kernel est exécutée

- L'instance est appelée work-item

- Identifiée par l'indice appelé global ID

- Tous les work-items exécutent le même code mais peuvent diverger

Exemple: addition de matrices (kernel)

```

40 _kernel void matrix add(float * a, float * b, float * c) {

41    int x = get_global_id(0);

42    int p = get_global_size(0);

43    int n = get_global_size(0);

44    int off = y*n + x;

46    c[off] = a[off] + b[off];

48 }

```

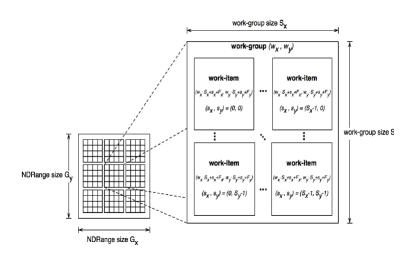

### OpenCL Modèle d'exécution

- L'espace d'indices est sub-divisé en work-groups

- 1, 2 ou 3 dimensions (la même que l'espace d'indices)

- Identifiés par un work-group ID

- Les work-items se voient attribuer un local ID au sein de leur work-group

- Un work-item peut être identifié de façon unique par :

- Son global ID

- L'ID de son work-group et son propre local ID

Modèle d'exécution : index space, work-groups, work-items...

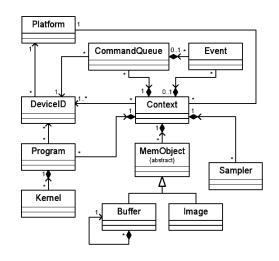

API hôte : diagramme de classes (source : spécification 1.2)

# OpenCL Contextes et files de commandes

- Les contextes pour l'exécution des codes sur accélérateurs incluent

- Devices Les accélérateurs utilisables par l'hôte

- Kernels Les noyaux de calculs exécutables par les accélérateurs

- Program Le code source et/ou les binaires des kernels

- Memory objects Les espaces mémoires manipulés par l'hôte et les accélérateurs. Les kernels ne peuvent accéder qu'à ces objets

- Les files de commandes (command queues) coordonnent les exécutions de commandes asynchrones

- Exécution de kernels

- Transferts de données

- Synchronisations

#### Files de commandes et évènements

- Les files de commandes peuvent être configurées

- In order Les commandes soumises seront exécutées successivement lorsque la précédente termine

- Out of order Les commandes sont exécutés successivement mais n'attendent pas que la précédente termine

- À chaque commande soumise est associé un évènement (event object)

- Gestion fine des dépendances entre commandes et évènements

### OpenCL Types de kernels

- OpenCL supporte deux types de kernels

- Kernels OpenCL écrits avec l'OpenCL C Language

- Kernels natifs dépendant de l'implémentation

- Certains accélérateurs ne supportent que l'un des deux types

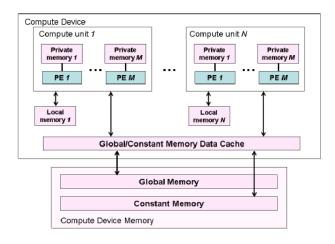

- Global memory

- Accessible en lecture/écriture par tous les work-items

- Accessible par l'hôte en lecture/écriture

- Constant memory

- Accessible en lecture seule par tous les work-items

- Accessible par l'hôte en lecture/écriture

- Local memory

- Mémoire locale à un work-group

- Partagée en lecture/écriture par les work-items du work-group

- Private memory

- Mémoire privée d'un work-item

- Global memory

- Accessible en lecture/écriture par tous les work-items

- Accessible par l'hôte en lecture/écriture

- Constant memory

- Accessible en lecture seule par tous les work-items

- Accessible par l'hôte en lecture/écriture

- Local memory

- Mémoire locale à un work-group

- Partagée en lecture/écriture par les work-items du work-group

- Private memory

- Mémoire privée d'un work-item

- Global memory

- Accessible en lecture/écriture par tous les work-items

- Accessible par l'hôte en lecture/écriture

- Constant memory

- Accessible en lecture seule par tous les work-items

- Accessible par l'hôte en lecture/écriture

- Local memory

- Mémoire locale à un work-group

- Partagée en lecture/écriture par les work-items du work-group

- Private memory

- Mémoire privée d'un work-item

- Global memory

- Accessible en lecture/écriture par tous les work-items

- Accessible par l'hôte en lecture/écriture

- Constant memory

- Accessible en lecture seule par tous les work-items

- Accessible par l'hôte en lecture/écriture

- Local memory

- Mémoire locale à un work-group

- Partagée en lecture/écriture par les work-items du work-group

- Private memory

- Mémoire privée d'un work-item

Modèle mémoire : allocation et accès

|        | Global                | Constant              | Local                 | Private           |

|--------|-----------------------|-----------------------|-----------------------|-------------------|

| Host   | Dynamic<br>allocation | Dynamic<br>allocation | Dynamic<br>allocation | No allocation     |

|        | Read / Write          | Read / Write          | No access             | No access         |

| Kernel | No allocation         | Static allocation     | Static allocation     | Static allocation |

|        | Read / Write          | Read-only             | Read / Write          | Read / Write      |

|        | access                | access                | access                | access            |

- OpenCL utilise un modèle mémoire à cohérence relâchée

- Au sein d'un work-item

- load/store consistency

- Local memory

- cohérence entre les work-items d'un work-group après une barrière

- Global memory

- cohérence entre les work-items d'un work-group après une barrière

- pas de cohérence entre les work-items de différents work-groups

- OpenCL utilise un modèle mémoire à cohérence relâchée

- Au sein d'un work-item

- load/store consistency

- Local memory

- cohérence entre les work-items d'un work-group après une barrière

- Global memory

- cohérence entre les work-items d'un work-group après une barrière

- pas de cohérence entre les work-items de différents work-groups

- OpenCL utilise un modèle mémoire à cohérence relâchée

- Au sein d'un work-item

- load/store consistency

- Local memory

- cohérence entre les work-items d'un work-group après une barrière

- Global memory

- cohérence entre les work-items d'un work-group après une barrière

- pas de cohérence entre les work-items de différents work-groups

- OpenCL utilise un modèle mémoire à cohérence relâchée

- Au sein d'un work-item

- load/store consistency

- Local memory

- cohérence entre les work-items d'un work-group après une barrière

- Global memory

- cohérence entre les work-items d'un work-group après une barrière

- pas de cohérence entre les work-items de différents work-groups

- Synchronisations entre work-items d'un work-group

- Barrières

- Tous les work-items doivent passer par chaque barrière

- Pas de mécanisme de synchronisation entre les work-groups

- Synchronisations entre les commandes

- Files de commandes en mode « in-order »

- Barrières dans les files de commandes

- Exécute les commandes après la barrière quand celles avant la barrière ont terminé

- Évènements

- À chaque commande soumise est associé un évènement

- Les commandes peuvent dépendre d'évènements

- Synchronisations entre work-items d'un work-group

- Barrières

- Tous les work-items doivent passer par chaque barrière

- Pas de mécanisme de synchronisation entre les work-groups

- Synchronisations entre les commandes

- Files de commandes en mode « in-order »

- Barrières dans les files de commandes

- Exécute les commandes après la barrière quand celles avant la barrière ont terminé

- Évènements

- À chaque commande soumise est associé un évènement

- Les commandes peuvent dépendre d'évènements

- Synchronisations entre work-items d'un work-group

- Barrières

- Tous les work-items doivent passer par chaque barrière

- Pas de mécanisme de synchronisation entre les work-groups

- Synchronisations entre les commandes

- Files de commandes en mode « in-order »

- Barrières dans les files de commandes

- Exécute les commandes après la barrière quand celles avant la barrière ont terminé

- Évènements

- À chaque commande soumise est associé un évènement

- Les commandes peuvent dépendre d'évènements

- Synchronisations entre work-items d'un work-group

- Barrières

- Tous les work-items doivent passer par chaque barrière

- Pas de mécanisme de synchronisation entre les work-groups

- Synchronisations entre les commandes

- Files de commandes en mode « in-order »

- Barrières dans les files de commandes

- Exécute les commandes après la barrière quand celles avant la barrière ont terminé

- Évènements

- À chaque commande soumise est associé un évènement

- Les commandes peuvent dépendre d'évènements

Exemple : somme des éléments d'un vecteur (kernel)

```

.d vector sum(float * v, float * res) +

q x = qet qlobal id(0);

int l x = get local id(0):

int b x = get_group_id(0);

int n = get global size(0);

_local v2[256];

v2[l x] = v[q x];

barrier(CLK LOCAL MEM FENCE);

for (i=128; i!=0; i/=2) {

if (l x < i) {

v2[l x] += v2[l x + i];

barrier(CLK LOCAL MEM FENCE);

if (l x == 0) {

res[b x] = v2[l x];

```

#### Exemple FAUX : tous les threads ne rencontrent pas la barrière

```

kernel void vector sum wrong(float * v, float * res) {

int g x = get global id(0);

int l x = get local id(0);

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

int b x = get group id(0);

int n = get global size(0);

local v2[256];

v2[l x] = v[g x];

barrier(CLK_LOCAL_MEM_FENCE);

for (i=128; i!=0; i/=2) {

if (l \times < i) {

v2[l x] += v2[l x + i];

barrier(CLK LOCAL MEM FENCE);

if (l x == 0) {

res[b x] = v2[l x];

```

### OpenCL Objets mémoire

- OpenCL supporte deux types d'objets mémoire

- Buffer et Image (regroupés sous le type cl\_mem)

- Buffer

- 1 dimension

- Collection d'éléments de n'importe quel type (int, float, structures...)

- Accessible directement (pointeur)

- Image

- 2 ou 3 dimensions

- Format prédéfini choisi parmi une liste

- Utilisée comme texture ou comme frame buffei

- Accessible à travers des fonctions prédéfinies

- Le format de stockage n'est pas forcément le même que le format utilisé par le kernel

### OpenCL Objets mémoire

- OpenCL supporte deux types d'objets mémoire

- Buffer et Image (regroupés sous le type cl\_mem)

- Buffer

- 1 dimension

- Collection d'éléments de n'importe quel type (int, float, structures...)

- Accessible directement (pointeur)

- Image

- 2 ou 3 dimensions

- Format prédéfini choisi parmi une liste

- Utilisée comme texture ou comme frame buffer

- Accessible à travers des fonctions prédéfinies

- Le format de stockage n'est pas forcément le même que le format utilisé par le kernel

### OpenCL Objets mémoire

- OpenCL supporte deux types d'objets mémoire

- Buffer et Image (regroupés sous le type cl\_mem)

- Buffer

- 1 dimension

- Collection d'éléments de n'importe quel type (int, float, structures...)

- Accessible directement (pointeur)

- Image

- 2 ou 3 dimensions

- Format prédéfini choisi parmi une liste

- Utilisée comme texture ou comme frame buffer

- Accessible à travers des fonctions prédéfinies

- Le format de stockage n'est pas forcément le même que le format utilisé par le kernel

### OpenCL Le framework OpenCL

- OpenCL Platform Layer

- Découverte des accélérateurs OpenCL et de leurs caractéristiques par l'hôte et création de contextes

- OpenCL Runtime

- Manipulation des contextes et autres entités

- OpenCL Compiler

- Compilation des kernels à exécuter sur les accélérateurs

### OpenCL Le framework OpenCL

- OpenCL Platform Layer

- Découverte des accélérateurs OpenCL et de leurs caractéristiques par l'hôte et création de contextes

- OpenCL Runtime

- Manipulation des contextes et autres entités

- OpenCL Compiler

- Compilation des kernels à exécuter sur les accélérateurs

### OpenCL Le framework OpenCL

- OpenCL Platform Layer

- Découverte des accélérateurs OpenCL et de leurs caractéristiques par l'hôte et création de contextes

- OpenCL Runtime

- Manipulation des contextes et autres entités

- OpenCL Compiler

- Compilation des kernels à exécuter sur les accélérateurs

### OpenCL API hôte : les plateformes

cl\_platform\_info = CL\_PLATFORM\_PROFILE, CL\_PLATFORM\_VERSION, CL\_PLATFORM\_NAME, CL\_PLATFORM\_VENDOR, CL\_PLATFORM\_EXTENSIONS

API hôte : les accélérateurs

```

cl_int

cl_device_type_device_type,

cl_uint num_entries,

cl_device_id *devices,

cl_device_id *devices,

cl_uint *num_devices)

cl_int

cl_device_id device,

cl_uint *num_devices

cl_uint *num_devices

cl_device_info param_name,

size_t param_value_size,

void *param_value,

size_ret)

```

### OpenCL API hôte : les accélérateurs

| cl_device_type             | Description                                         |  |

|----------------------------|-----------------------------------------------------|--|

| CL_DEVICE_TYPE_CPU         | An OpenCL device that is the host processor. The    |  |

|                            | host processor runs the OpenCL implementations      |  |

|                            | and is a single or multi-core CPU.                  |  |

| CL_DEVICE_TYPE_GPU         | An OpenCL device that is a GPU. By this we mean     |  |

|                            | that the device can also be used to accelerate a 3D |  |

|                            | API such as OpenGL or DirectX.                      |  |

| CL_DEVICE_TYPE_ACCELERATOR | Dedicated OpenCL accelerators (for example the      |  |

|                            | IBM CELL Blade). These devices communicate          |  |

|                            | with the host processor using a peripheral          |  |

|                            | interconnect such as PCIe.                          |  |

| CL_DEVICE_TYPE_CUSTOM      | Dedicated accelerators that do not support programs |  |

|                            | written in OpenCL C.                                |  |

| CL_DEVICE_TYPE_DEFAULT     | The default OpenCL device in the system. The        |  |

|                            | default device cannot be a                          |  |

|                            | CL_DEVICE_TYPE_CUSTOM device.                       |  |

| CL_DEVICE_TYPE_ALL         | All OpenCL devices available in the system except   |  |

|                            | CL_DEVICE_TYPE_CUSTOM devices                       |  |

### OpenCL API hôte : informations sur les accélérateurs

| cl_device_info                      | Return Type    | Description                                                                                                                                                                                                                     |

|-------------------------------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CL_DEVICE_TYPE                      | cl_device_type | The OpenCL device type. Currently supported values are:                                                                                                                                                                         |

|                                     |                | CL_DEVICE_TYPE_CPU, CL_DEVICE_TYPE_GPU, CL_DEVICE_TYPE_ACCELERATOR, CL_DEVICE_TYPE_DEFAULT, a combination of the above types or CL_DEVICE_TYPE_CUSTOM                                                                           |

| CL_DEVICE_VENDOR_ID                 | cl_uint        | A unique device vendor identifier. An<br>example of a unique device identifier could be<br>the PCIe ID.                                                                                                                         |

| CL_DEVICE_MAX_COMPUTE_UNITS         | cl_uint        | The number of parallel compute units on the OpenCL device. A work-group executes on a single compute unit. The minimum value is 1.                                                                                              |

| CL_DEVICE_MAX_WORK_ITEM_ DIMENSIONS | cl_uint        | Maximum dimensions that specify the global and local work-item IDs used by the data parallel execution model. (Refer to cIEnqueueNDRangeKerne)). The minimum value is 3 for devices that are not of type CL_DEVICE_TYPE_CUSTOM. |

| CL_DEVICE_MAX_WORK_ITEM_SIZES              | size_t [] | Maximum number of work-items that can be specified in each dimension of the work-group to clEnqueueNDRangeKernel.                                                                                          |

|--------------------------------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                            |           | Returns n size_t entries, where n is the value returned by the query for CL_DEVICE_MAX_WORK_ITEM_DIMENSIC NS.                                                                                              |

|                                            |           | The minimum value is (1, 1, 1) for devices that are not of type CL_DEVICE_TYPE_CUSTOM.                                                                                                                     |

| CL_DEVICE_MAY_WORK_GROUP_SIZE              | size_t    | Maximum number of work-items in a work-<br>group executing a kernel on a single compute<br>unit, using the data parallel execution model.<br>(Refer to ciEnqueueNDRangeKernel).<br>The minimum value is 1. |

| CL_DEVICE_PREFERRED_<br>VECTOR_WIDTH_CHAR  | cl_uint   | Preferred native vector width size for built-in<br>scalar types that can be put into vectors. The                                                                                                          |

| CL_DEVICE_PREFERRED_<br>VECTOR_WIDTH_SHORT |           | vector width is defined as the number of<br>scalar elements that can be stored in the                                                                                                                      |

| CL_DEVICE_PREFERRED_<br>VECTOR_WIDTH_INT   |           | vector.                                                                                                                                                                                                    |

| CL_DEVICE PREFERED_ VECTOR_WIDTH_LONG  CL_DEVICE_PREFERED_ VECTOR_WIDTH_FLOAT  CL_DEVICE_PREFERED_ VECTOR_WIDTH_DOUBLE  CL_DEVICE_PREFERED_ VECTOR_WIDTH_HALF                                                                                                                                                                                          |         | If double precision is not supported, CL_DEVICE_PREFERRED_VECTOR_WIDTH_DO UBLE must return 0.  If the cl_khr_fp16 extension is not supported, CL_DEVICE_PREFERRED_VECTOR_WIDTH_HA LF must return 0.                                                                                                                              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VECTOR WIDTH HALF CL_DEVICE_NATIVE_ VECTOR_WIDTH_CHAR CL_DEVICE_NATIVE VECTOR_WIDTH_SHORT CL_DEVICE_NATIVE VECTOR_WIDTH_INT CL_DEVICE_NATIVE VECTOR_WIDTH_LONG CL_DEVICE_NATIVE VECTOR_WIDTH_FLOAT CL_DEVICE_NATIVE VECTOR_WIDTH_DOUBLE CL_DEVICE_NATIVE VECTOR_WIDTH_DOUBLE CL_DEVICE_NATIVE VECTOR_WIDTH_DOUBLE CL_DEVICE_NATIVE VECTOR_WIDTH_HOUBLE | cl_uint | Returns the native ISA vector width. The vector width is defined as the number of scalar elements that can be stored in the vector.  If double precision is not supported, CL_DEVICE_NATIVE_VECTOR_WIDTH_DOUBLE must return 0.  If the cl_thr_fp16 extension is not supported, CL_DEVICE_NATIVE_VECTOR_WIDTH_HALF must return 0. |

| CL_DEVICE_MAX_CLOCK_<br>FREQUENCY | cl_uint  | Maximum configured clock frequency of the device in MHz.                                                                                                                                        |

|-----------------------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CL_DEVICE_ADDRESS_BITS            | cl_uint  | The default compute device address space<br>size specified as an unsigned integer value in<br>bits. Currently supported values are 32 or 64<br>bits.                                            |

| CL_DEVICE_MAX_MEM_ALLOC_SIZE      | cl_ulong | Max size of memory object allocation in bytes. The minimum value is max (1/4 <sup>th</sup> of CL_DEVICE_GLOBAL_MEM_SIZE, 128*1024*1024) for devices that are not of type CL_DEVICE_TYPE_CUSTOM. |

| CL_DEVICE_IMAGE_SUPPORT           | cl_bool  | Is CL_TRUE if images are supported by the<br>OpenCL device and CL_FALSE otherwise.                                                                                                              |

| CL_DEVICE_MAX_READ_IMAGE_ARGS     | cl_uint  | Max number of simultaneous image objects that can be read by a kernel. The minimum value is 128 if CL_DEVICE_IMAGE_SUPPORT is CL_TRUE.                                                          |

| CL_DEVICE_MAX_WRITE_IMAGE_ARGS    | cl_uint  | Max number of simultaneous image objects that can be written to by a kernel. The minimum value is 8 if                                                                                          |

| CL_DEVICE_MEM_BASE_ADDR_ALIGN           | cl_uint                      | The minimum value is the size (in bits) of the largest OpenCL built-in data type supported by the device (long16 in FULL profile, long16 or int16 in EMBEDDED profile) for devices that are not of type CL_DEVICE_TYPE_CUSTOM. |

|-----------------------------------------|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CL_DEVICE_GLOBAL_MEM_CACHE_<br>TYPE     | cl_device_mem_<br>cache_type | Type of global memory cache supported. Valid values are: CL_NONE, CL_READ_ONLY_CACHE and CL_READ_WRITE_CACHE.                                                                                                                  |

| CL_DEVICE_GLOBAL_MEM_CACHELINE_<br>SIZE | cl_uint                      | Size of global memory cache line in bytes.                                                                                                                                                                                     |

| CL_DEVICE_GLOBAL_MEM_CACHE_<br>SIZE     | cl_ulong                     | Size of global memory cache in bytes.                                                                                                                                                                                          |

| CL_DEVICE_GLOBAL_MEM_SIZE               | cl_ulong                     | Size of global device memory in bytes.                                                                                                                                                                                         |

|                                         |                              |                                                                                                                                                                                                                                |

| CL_DEVICE_MAX_CONSTANT_                 | cl_ulong                     | Max size in bytes of a constant buffer                                                                                                                                                                                         |

| r                           |                              |                                                                                                                                                         |

|-----------------------------|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| BUFFER_SIZE                 |                              | allocation. The minimum value is 64 KB for                                                                                                              |

|                             |                              | devices that are not of type                                                                                                                            |

|                             |                              | CL_DEVICE_TYPE_CUSTOM.                                                                                                                                  |

| CL_DEVICE_MAX_CONSTANT_ARGS | cl_uint                      | Max number of arguments declared with theconstant qualifier in a kernel. The minimum value is 8 for devices that are not of type CL_DEVICE_TYPE_CUSTOM. |

|                             |                              |                                                                                                                                                         |

| CL_DEVICE_LOCAL_MEM_TYPE    | cl_device_<br>local_mem_type | Type of local memory supported. This can be set to CL_LOCAL implying dedicated local memory storage such as SRAM, or CL_GLOBAL.                         |

|                             |                              | For custom devices, CL_NONE can also be returned indicating no local memory support.                                                                    |

| CL_DEVICE_LOCAL_MEM_SIZE    | cl_ulong                     | Size of local memory arena in bytes. The minimum value is 32 KB for devices that are not of type CL_DEVICE_TYPE_CUSTOM.                                 |

| CL_DEVICE_ERROR_CORRECTION_<br>SUPPORT   | cl_bool | Is CL_TRUE if the device implements error correction for all accesses to compute device memory (global and constant). Is CL_FALSE if the device does not implement such error correction. |

|------------------------------------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                          |         |                                                                                                                                                                                           |

| CL_DEVICE_HOST_UNIFIED_<br>MEMORY        | cl_bool | Is CL_TRUE if the device and the host have a<br>unified memory subsystem and is CL_FALSE<br>otherwise.                                                                                    |

| CL_DEVICE_PROFILING_TIMER_<br>RESOLUTION | size_t  | Describes the resolution of device timer. This is measured in nanoseconds. Refer to section. 5.12 for details.                                                                            |

|                                          |         |                                                                                                                                                                                           |

| CL_DEVICE_ENDIAN_LITTLE                  | cl_bool | Is CL_TRUE if the OpenCL device is a little<br>endian device and CL_FALSE otherwise.                                                                                                      |

| CL_DEVICE_PLATFORM | cl_platform_id | The platform associated with this device. |

|--------------------|----------------|-------------------------------------------|

|                    |                |                                           |

| CL_DEVICE_NAME     | char[]         | Device name string.                       |

| CL_DEVICE_VENDOR   | char[]         | Vendor name string                        |

#### OpenCL API hôte : les contextes

#### API hôte : informations sur les contextes

cl\_int clGetContextInfo (cl\_context context,

cl\_context\_info param\_name,

size\_t\_param\_value\_size,

void \*param\_value,

size\_t \*param\_value\_size\_ret)

| cl_context_info                             | Return Type             | Information returned in param_value                                                            |

|---------------------------------------------|-------------------------|------------------------------------------------------------------------------------------------|

| CL_CONTEXT_REFERENCE_<br>COUNT <sup>8</sup> | cl_uint                 | Return the context reference count.                                                            |

| CL_CONTEXT_NUM_<br>DEVICES                  | cl_uint                 | Return the number of devices in context                                                        |

| CL_CONTEXT_DEVICES                          | cl_device_id[]          | Return the list of devices in context.                                                         |

| CL_CONTEXT_PROPERTIES                       | cl_context_properties[] | Return the <i>properties</i> argument specified in clCreateContext or clCreateContextFromType. |

# OpenCL API hôte : les files de commandes

| Command-Queue Properties                   | Description                                                                                                                                                                                                        |

|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CL_QUEUE_OUT_OF_ORDER_EXEC_MODE_<br>ENABLE | Determines whether the commands queued in the command-queue are executed in-order or out-of-order. If set, the commands in the command-queue are executed out-of-order. Otherwise, commands are executed in-order. |

|                                            | For a detailed description about CL_QUEUE_OUT_OF_ORDER_EXEC_MODE_ENABLE, refer to section 5.11.                                                                                                                    |

| CL_QUEUE_PROFILING_ENABLE                  | Enable or disable profiling of commands in<br>the command-queue. If set, the profiling of<br>commands is enabled. Otherwise profiling<br>of commands is disabled.                                                  |

| cl_mem_flags      | Description                                                                                            |

|-------------------|--------------------------------------------------------------------------------------------------------|

| CL_MEM_READ_WRITE | This flag specifies that the memory object will be read and written by a kernel. This is the default.  |

| CL_MEM_WRITE_ONLY | This flag specifies that the memory object will be written but not read by a kernel.                   |

|                   | Reading from a buffer or image object created with CL_MEM_WRITE_ONLY inside a kernel is undefined.     |

|                   | CL_MEM_READ_WRITE and CL_MEM_WRITE_ONLY are mutually exclusive.                                        |

| CL_MEM_READ_ONLY  | This flag specifies that the memory object is a read-<br>only memory object when used inside a kernel. |

|                   | Writing to a buffer or image object created with CL_MEM_READ_ONLY inside a kernel is undefined.        |

|                   | CL_MEM_READ_WRITE or CL_MEM_WRITE_ONLY and CL_MEM_READ_ONLY are mutually exclusive.                    |

| CL_MEM_COPY_HOST_PTR   | This flag is valid only if host ptr is not NULL. If specified, it indicates that the application wants the OpenCL implementation to allocate memory for the memory object and copy the data from memory referenced by host_ptr.                                                                                                    |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                        | CL_MEM_COPY_HOST_PTR and CL_MEM_USE_HOST_PTR are mutually exclusive.                                                                                                                                                                                                                                                               |

|                        | CL_MEM_COPY_HOST_PTR can be used with CL_MEM_ALLOC_HOST_PTR to initialize the contents of the cl_mem object allocated using host-accessible (e.g. PCIe) memory.                                                                                                                                                                    |

| CL_MEM_HOST_WRITE_ONLY | This flag specifies that the host will only write to the memory object (using OpenCL APIs that enqueue a write or a map for write). This can be used to optimize write access from the host (e.g. enable write-combined allocations for memory objects for devices that communicate with the host over a system bus such as PCIe). |

| CL_MEM_HOST_READ_ONLY | This flag specifies that the host will only read the memory object (using OpenCL APIs that enqueue a read or a map for read). |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------|

|                       | CL_MEM_HOST_WRITE_ONLY and                                                                                                    |

|                       | CL_MEM_HOST_READ_ONLY are mutually                                                                                            |

|                       | exclusive.                                                                                                                    |

| CL_MEM_HOST_NO_ACCESS | This flag specifies that the host will not read or write                                                                      |

|                       | the memory object.                                                                                                            |

|                       |                                                                                                                               |

|                       | CL_MEM_HOST_WRITE_ONLY or                                                                                                     |

|                       | CL_MEM_HOST_READ_ONLY and                                                                                                     |

|                       | CL_MEM_HOST_NO_ACCESS are mutually                                                                                            |

|                       | exclusive.                                                                                                                    |

#### API hôte : les transferts de données hôte <-> device

```

cl int clEnqueueReadBuffer (cl command queue command queue.

cl mem buffer,

cl bool blocking read,

size t offset.

size t size,

void *ptr,

cl uint num events in wait list,

const cl event *event wait list,

cl event *event)

cl int clEnqueueWriteBuffer (cl command queue command queue,

cl mem buffer,

cl bool blocking write.

size toffset,

size t size.

const void *ptr.

cl uint num events in wait list,

const cl event *event wait list.

cl event *event)

```

API hôte : les transferts de données buffer -> buffer

```

cl_int clEnqueueCopyBuffer (cl_command_queue command_queue,

cl_mem src_buffer,

cl_mem dst_buffer,

size_t src_offset,

size_t dst_offset,

size_t size,

cl_unt num_events_in_wait_list,

const cl_event *event_wait_list,

cl_event *event)

```

API hôte : les transferts de données hôte -> buffer (avec padding)

API hôte : les transferts de données buffer -> hôte (avec padding)

```

cl_int clEnqueueReadBufferRect (cl_command_queue command_queue,

cl_mem buffer,

cl_bool blocking_read,

const size_t *buffer_origin,

const size_t *host_origin,

const size_t *tegion,

size_t buffer_row_pitch,

size_t buffer_slice_pitch,

size_t host_row_pitch,

size_t host_row_pitch,

void *ptr,

cl_uint num_events_in_wait_list,

const_d_event *event_wait_list,

cl_event *event)

```

API hôte : les transferts de données buffer -> buffer (avec padding)

```

cl_int clEnqueueCopyBufferRect (cl_command_queue command_queue,

cl_mem src_buffer,

cl_mem dst_buffer,

const size_t *src_origin,

const size_t *region,

size_t src_row_pitch,

size_t src_slice_pitch,

size_t src_slice_pitch,

size_t dst_slice_pitch,

cl_min_mum_events_in_wait_list,

const cl_event *event_wait_list,

cl_event *event)

```

API hôte : mapping en mémoire hôte

```

void * clEnqueueMapBuffer (cl command queue command queue,

cl mem buffer.

cl bool blocking map.

cl map flags map flags,

size toffset.

size t size,

cl uint num events in wait list,

const cl event *event wait list.

cl event *event.

cl int *errcode ret)

cl int clEnqueueUnmapMemObject (cl command queue command queue,

cl mem memobi,

void *mapped ptr.

cl uint num events in wait list,

const cl event *event wait list.

cl event *event)

```

#### API hôte : mapping en mémoire hôte

| cl_map_flags | Description                                                                                                                                                                          |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CL_MAP_READ  | This flag specifies that the region being mapped<br>in the memory object is being mapped for<br>reading.                                                                             |

|              | The pointer returned by clEnqueueMap{Buffer   Image} is guaranteed to contain the latest bits in the region being mapped when the clEnqueueMap{Buffer   Image} command has completed |

| CL_MAP_WRITE | This flag specifies that the region being mapped<br>in the memory object is being mapped for<br>writing.                                                                             |

API hôte : mapping en mémoire hôte

|                                | The pointer returned by clEnqueueMap{Buffer   Image} is guaranteed to contain the latest bits in the region being mapped when the clEnqueueMap{Buffer |

|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                | to contain the latest bits in the region being mapped when the clEnqueueMap{Buffer                                                                    |

|                                | mapped when the clEnqueueMap{Buffer                                                                                                                   |

|                                |                                                                                                                                                       |

|                                |                                                                                                                                                       |

|                                | Image) command has completed                                                                                                                          |

| CL MAP WRITE INVALIDATE REGION | This flag specifies that the region being mapped                                                                                                      |

|                                | in the memory object is being mapped for                                                                                                              |

|                                |                                                                                                                                                       |

|                                | writing.                                                                                                                                              |

|                                |                                                                                                                                                       |

|                                | The contents of the region being mapped are to                                                                                                        |

|                                | be discarded. This is typically the case when                                                                                                         |

|                                | the region being mapped is overwritten by the                                                                                                         |

|                                | host. This flag allows the implementation to no                                                                                                       |

|                                | longer guarantee that the pointer returned by                                                                                                         |

|                                | clEnqueueMap{Buffer   Image} contains the                                                                                                             |

|                                | latest bits in the region being mapped which can                                                                                                      |

|                                |                                                                                                                                                       |

|                                | be a significant performance enhancement.                                                                                                             |

|                                |                                                                                                                                                       |

|                                | CL_MAP_READ or CL_MAP_WRITE and                                                                                                                       |

|                                | CL_MAP_WRITE_INVALIDATE_REGION are                                                                                                                    |

|                                | mutually exclusive                                                                                                                                    |

## OpenCL API hôte : migration d'objets mémoire

| cl_mem_migration flags                      | Description                                                                                                                                                                                                                                                |

|---------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CL_MIGRATE_MEM_OBJECT_HOST                  | This flag indicates that the specified set of memory objects are to be migrated to the host, regardless of the target command-queue.                                                                                                                       |

| CL_MIGRATE_MEM_OBJECT_<br>CONTENT_UNDEFINED | This flag indicates that the contents of the set of memory objects are undefined after migration. The specified set of memory objects are migrated to the device associated with command queue without incurring the overhead of migrating their contents. |

- Les objets mémoire sont associés à un contexte, pas à un device

- Besoin de forcer l'allocation sur un device particulier

#### API hôte : création de programmes

```

cl program

clCreateProgramWithSource (cl context context,

cl uint count,

const char **strings,

const size t *lengths.

cl int *errcode ret)

cl program

clCreateProgramWithBinary (cl context context,

cl uint num devices.

const cl device id *device list,

const size t *lengths,

const unsigned char **binaries,

cl int *binary status,

cl int *errcode ret)

cl int

clReleaseProgram (cl program program)

```

#### API hôte : compilation de programmes + édition de liens

```

cl_int clBuildProgram (cl_program program,

cl_uint num_devices,

const cl_device_id *device_list,

const char *options,

void (CL_CALLBACK *pfn_notify)(cl_program program,

void *user_data),

void *user_data)

```

#### API hôte : compilation de programmes

```

cl_int clCompileProgram (cl_program program,

cl_uint num_devices,

const cl_device_id *device_list,

const char *options,

cl_uint num_input_headers,

const cl_program *input_headers,

const char **header include_names,

void (CL_CALLBACK *pfn_notify)(cl_program program,

void *user_data),

void *user_data)

```

API hôte : édition de liens

API hôte : informations sur la compilation

cl\_int clGetProgramBuildInfo (cl\_program program,

cl\_device\_id device,

cl\_program\_build\_info param\_name,

size\_t param\_value\_size,

void \*param\_value,

size\_t \*param\_value\_size\_ret)

# OpenCL API hôte : informations sur la compilation

| cl_program_buid_info        | Return Type     | Info. returned in param_value                                                                                                                                                                  |

|-----------------------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CL_PROGRAM_BUILD_<br>STATUS | cl_build_status | Returns the build, compile or link status, whichever was performed last on program for device.                                                                                                 |

|                             |                 | This can be one of the following:                                                                                                                                                              |

|                             |                 | CL_BUILD_NONE. The build status returned if no clBuildProgram, clCompileProgram or clLinkProgram has been performed on the specified program object for device.                                |

|                             |                 | CL_BUILD_ERROR. The build status returned if clBuildProgram, clCompileProgram or clLinkProgram whichever was performed last on the specified program object for device generated an error.     |

|                             |                 | CL_BUILD_SUCCESS. The build status returned if clBuildProgram, clCompileProgram or clLinkProgram whichever was performed last on the specified program object for device was successful.       |

|                             |                 | CL_BUILD_IN_PROGRESS. The build status returned if clBuildProgram, clCompileProgram or clLinkProgram whichever was performed last on the specified program object for device has not finished. |

#### API hôte : informations sur la compilation

| CL_PROGRAM_BUILD_<br>LOG | char[] | Return the build, compile or link log for clBuildProgram, clCompileProgram or clLinkProgram whichever was performed last on program for device. |

|--------------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------|

|                          |        | If build status of program for device is CL_BUILD_NONE, an empty string is returned.                                                            |

#### OpenCL API hôte : création de kernels

```

cl_kernel | clCreateKernel (cl_program program, const char *kernel_name, cl_int *errcode_ret) | cl_int *errcode_ret | cl_int *errcode_ret | cl_int num_kernels, cl_kernel *kernels, cl_wint *num_kernels_ret | cl_int | clReleaseKernel (cl_kernel kernel)

```

Un kernel est une fonction qualifiée par \_\_kernel dans le code du programme

## OpenCL API hôte : paramètres des kernels

```

cl_int clSetKernelArg (cl_kernel kernel,

cl_uint arg_index,

size_t arg_size,

const void *arg_value)

```

- arg\_value peut pointer vers un cl\_mem

- Pour les paramètres en mémoire locale

- arg\_value est à NULL

- arg\_size indique la quantité de mémoire à allouer

API hôte : exécution de kernels

cl int

${\bf clEnqueueNDRangeKernel}~({\bf cl\_command\_queue}~command\_queue,$

cl\_kernel kernel,

cl\_uint work\_dim,

const size\_t \*global\_work\_offset,

const size\_t \*lobal\_work\_size,

const size\_t \*local\_work\_size,

cl\_uint num\_events\_in\_wait\_list,

const cl\_event \*event\_wait\_list,

cl\_event \*event]

API hôte : exécution de kernels natifs

#### OpenCL API hôte : évènements

- Les évènements sont associés aux commandes soumises

- Les commandes peuvent dépendre d'évènements

- Elles sont exécutées quand les commandes associées aux évènements sont terminées (état CL\_COMPLETE).

```

cl_event

clCreateUserEvent (cl_context context, cl_int *errcode_ret)

cl_int